Clock Domain Crossing (CDC) is a critical aspect of digital design that plays a pivotal role in ensuring the reliability and performance of modern integrated circuits. As technology advances and chip designs become more complex, the importance of understanding and implementing effective CDC strategies has grown exponentially. This article delves into the intricacies of CDC, providing a comprehensive guide for professionals and job seekers in the field of VLSI design and digital engineering.

Whether you're preparing for a technical interview or looking to enhance your knowledge of CDC concepts, this resource covers essential topics, common interview questions, and practical scenarios that will help you navigate the challenges of working with multiple clock domains. From basic definitions to advanced techniques, we'll explore the fundamental principles and best practices that underpin successful CDC design.

Introduction to Clock Domain Crossing (CDC)

Clock Domain Crossing is a phenomenon that occurs in digital systems when signals traverse from one clock domain to another. This transition can lead to various issues if not handled properly, making CDC a crucial consideration in modern chip design.

Definition of Clock Domain Crossing

Clock Domain Crossing refers to the transfer of data between two different clock domains within a digital system. A clock domain is a portion of a circuit that operates synchronously with respect to a single clock signal. When data moves between domains with different clock frequencies or phases, special care must be taken to ensure reliable data transfer.

Importance of CDC in Digital Design

The significance of CDC in digital design cannot be overstated. As integrated circuits become more complex and incorporate multiple functionalities, they often require different clock domains to optimize performance and power consumption. Proper handling of CDC is essential for:

- Ensuring data integrity across different parts of the system

- Preventing metastability issues that can lead to system failures

- Optimizing power consumption by allowing different parts of the chip to operate at their ideal frequencies

- Enabling modular design and integration of IP blocks with different timing requirements

Overview of Challenges in CDC

Designing for Clock Domain Crossing presents several challenges that engineers must address:

- Metastability: The primary concern in CDC, where signals can enter an unstable state when sampled near clock edges.

- Data coherency: Ensuring that multi-bit data is transferred correctly and maintains its integrity.

- Timing constraints: Meeting setup and hold times across different clock domains.

- Latency: Managing the delay introduced by synchronization techniques.

- Verification: Developing robust test strategies to validate CDC implementations.

Understanding these challenges is crucial for developing effective CDC solutions and preparing for technical interviews in the field.

Common Clock Domain Crossing Interview Questions

When preparing for interviews that focus on CDC, it's essential to be well-versed in both basic concepts and more advanced topics. This section covers a range of questions you might encounter, along with expert answers to help you formulate your own responses.

Basic Concepts of Clock Domain Crossing

What is Clock Domain Crossing?

Sample Question: Can you explain what Clock Domain Crossing is and why it's important in digital design?

Expert Answer: Clock Domain Crossing (CDC) occurs when a signal in a digital circuit transitions from one clock domain to another. This happens when two parts of a system operate on different clock frequencies or phases. CDC is crucial in digital design because it ensures reliable data transfer between these different clock domains, preventing issues like metastability, data corruption, and system failures. Proper CDC handling is essential for maintaining data integrity and overall system reliability in complex digital designs that incorporate multiple clock domains.

Why is CDC important in VLSI design?

Sample Question: Discuss the importance of Clock Domain Crossing in VLSI design.

Expert Answer: CDC is of paramount importance in VLSI design for several reasons:

- System Integration: Modern VLSI designs often incorporate multiple functional blocks, each potentially operating at different clock frequencies. CDC ensures seamless integration of these blocks.

- Performance Optimization: Different parts of a chip may require different clock speeds for optimal performance. CDC allows designers to implement these varying clock domains effectively.

- Power Management: CDC enables the implementation of power-saving techniques like dynamic frequency scaling, where different parts of the chip can operate at reduced frequencies when full performance isn't needed.

- Reliability: Proper CDC handling prevents data corruption and system instability that can arise from metastability issues when signals cross clock domains.

- Modular Design: CDC techniques allow for more modular design approaches, enabling the reuse of IP blocks with different timing requirements.

- Meeting Timing Constraints: In complex designs, CDC helps in meeting overall timing constraints by allowing different parts of the system to operate at their optimal frequencies.

Understanding and implementing effective CDC strategies is thus critical for creating robust, high-performance VLSI designs.

Explain the synchronization techniques used in CDC.

Sample Question: What are the common synchronization techniques used in Clock Domain Crossing, and how do they work?

Expert Answer: Several synchronization techniques are commonly used in CDC:

- Double Flop Synchronizer:

- This is the most basic and widely used technique.

- It involves using two flip-flops in series in the receiving clock domain.

- The first flip-flop may enter metastability, but the second provides additional time for the signal to stabilize.

- It's simple to implement but introduces a latency of two clock cycles.

- Gray Code Counters:

- Used for transferring multi-bit counters across clock domains.

- Gray code ensures that only one bit changes at a time, reducing the risk of capturing an invalid intermediate state.

- Handshaking Protocols:

- Involves using request and acknowledge signals between the sending and receiving domains.

- Ensures data is only transferred when both domains are ready, preventing data loss or corruption.

- FIFO (First-In-First-Out) Buffers:

- Used for transferring multiple data items or streams across clock domains.

- Write and read operations occur in different clock domains, with separate full and empty flags to manage data flow.

- Pulse Synchronization:

- Used for transferring single-cycle pulses across clock domains.

- Involves stretching the pulse in the source domain and then synchronizing it in the destination domain.

- MUX-based Synchronizers:

- Used when multiple signals need to be synchronized to a single clock domain.

- Involves multiplexing the signals and then synchronizing the multiplexed output.

Each technique has its advantages and is chosen based on the specific requirements of the design, such as latency tolerance, data width, and the relationship between the clock frequencies involved.

Technical Questions Related to CDC

What are the major issues associated with Clock Domain Crossing?

Sample Question: Identify and explain the primary challenges encountered in Clock Domain Crossing.

Expert Answer: The major issues associated with Clock Domain Crossing include:

- Metastability:

- This is the primary concern in CDC.

- Occurs when a signal is sampled too close to its transition, potentially causing the flip-flop to enter an unstable state.

- Can lead to unpredictable behavior and system failures.

- Data Coherency:

- Ensuring that multi-bit data is transferred correctly and maintains its integrity across clock domains.

- Preventing the capture of intermediate states when multiple bits are changing.

- Timing Violations:

- Meeting setup and hold time requirements across different clock domains can be challenging.

- Violations can lead to data corruption or metastability.

- Latency:

- Synchronization techniques often introduce additional latency.

- Managing and minimizing this latency while ensuring reliable data transfer is crucial.

- Data Loss or Duplication:

- In asynchronous transfers, there's a risk of losing data or sampling the same data multiple times.

- Verification Complexity:

- CDC issues are often difficult to detect and debug.

- Requires specialized verification techniques and tools.

- Clock Skew and Jitter:

- Variations in clock arrival times can exacerbate CDC issues.

- Jitter in clock signals can reduce the available timing margins.

- Power Consumption:

- CDC circuits can contribute to increased power consumption, especially in designs with numerous clock domains.

- Area Overhead:

- Implementing robust CDC solutions often requires additional logic, impacting the overall chip area.

- Scalability:

- As designs grow more complex with multiple clock domains, managing CDC becomes increasingly challenging.

Addressing these issues requires a combination of careful design techniques, appropriate synchronization methods, and thorough verification strategies.

How does metastability affect Clock Domain Crossing?

Sample Question: Explain the concept of metastability and its impact on Clock Domain Crossing.

Expert Answer: Metastability is a critical phenomenon in Clock Domain Crossing that can significantly impact the reliability of digital systems. Here's a detailed explanation:

- Definition of Metastability:

- Metastability occurs when a flip-flop samples its input signal at or very close to its transition time.

- In this situation, the flip-flop's output may oscillate or settle to an unpredictable state for an indeterminate amount of time.

- Causes in CDC:

- In CDC scenarios, metastability is likely because the data signal from one clock domain is asynchronous to the receiving clock domain.

- This asynchronous relationship means there's always a chance that the data will change very close to the sampling edge of the receiving clock.

- Impact on CDC:

- Data Corruption: Metastability can cause the receiving flip-flop to capture an incorrect value, leading to data corruption.

- Propagation of Errors: If a metastable state resolves to an incorrect value, this error can propagate through the system.

- System Instability: In severe cases, metastability can cause system-wide failures or unpredictable behavior.

- Increased Latency: Waiting for a metastable signal to resolve can introduce additional, unpredictable delays.

- Probability and MTBF:

- The probability of a metastable event occurring decreases exponentially with time.

- Designers often calculate the Mean Time Between Failures (MTBF) to assess the risk of metastability-induced errors.

- Mitigation Strategies:

- Synchronizers: Using multi-stage synchronizers (e.g., double-flop synchronizers) to allow more time for metastable states to resolve.

- Timing Margins: Ensuring adequate setup and hold times to reduce the probability of metastability.

- Clock Domain Partitioning: Minimizing the number of CDC paths in the design.

- Design Considerations:

- Choosing appropriate flip-flop characteristics (e.g., higher metastability resistance).

- Implementing robust CDC protocols that can tolerate occasional metastable events.

- Verification Challenges:

- Metastability is non-deterministic, making it challenging to verify through traditional simulation methods.

- Specialized CDC verification tools and techniques are often required.

Understanding and addressing metastability is crucial in CDC design to ensure the reliability and stability of digital systems that operate across multiple clock domains.

Can you explain the concept of setup and hold time in CDC?

Sample Question: How do setup and hold times relate to Clock Domain Crossing, and why are they important?

Expert Answer: Setup and hold times are critical timing parameters in digital circuits, and they play a crucial role in Clock Domain Crossing scenarios. Here's a detailed explanation:

- Setup Time:

- Definition: The minimum time before the clock edge that the data must be stable for reliable capture.

- In CDC: Ensuring adequate setup time is challenging because the data signal is asynchronous to the receiving clock.

- Hold Time:

- Definition: The minimum time after the clock edge that the data must remain stable.

- In CDC: Hold time violations can occur if the data changes too quickly after being sampled by the receiving clock.

- Importance in CDC:

- Reliability: Meeting setup and hold times is crucial for reliable data transfer across clock domains.

- Metastability Prevention: Adequate timing margins reduce the probability of metastability.

- Data Integrity: Proper setup and hold times ensure that the correct data is captured.

- Challenges in CDC:

- Asynchronous Nature: The asynchronous relationship between clock domains makes it difficult to guarantee timing requirements.

- Clock Skew: Variations in clock arrival times can affect available setup and hold margins.

- Process Variations: Manufacturing variations can impact actual setup and hold times.

- Design Considerations:

- Synchronizer Design: Multi-stage synchronizers provide additional time to meet setup and hold requirements.

- Timing Analysis: Static Timing Analysis (STA) tools are used to verify setup and hold times across CDC paths.

- Margin Addition: Designers often add extra margin to account for uncertainties in CDC paths.

- Impact on Performance:

- Latency: Ensuring adequate setup and hold times may require additional synchronization stages, increasing latency.

- Clock Frequency Limitations: The need to meet timing requirements can limit the maximum operating frequency of the system.

- Verification:

- CDC-specific timing checks are crucial in verifying setup and hold times across clock domains.

- Specialized CDC verification tools may be used to analyze and validate timing in CDC paths.

- Trade-offs:

- Designers must balance the need for reliable data transfer with performance requirements when considering setup and hold times in CDC design.

Understanding and managing setup and hold times in CDC scenarios is essential for creating robust, reliable digital systems that operate across multiple clock domains.

What are the common methods to handle metastability in CDC?

Sample Question: Describe the techniques commonly used to mitigate metastability issues in Clock Domain Crossing.

Expert Answer: Several methods are employed to handle metastability in Clock Domain Crossing:

- Double Flop Synchronizer:

- The most common and straightforward technique.

- Uses two flip-flops in series in the receiving clock domain.

- The first flip-flop may enter metastability, but the second provides additional time for the signal to stabilize.

- Pros: Simple, effective for single-bit signals.

- Cons: Introduces a two-cycle latency.

- Triple Flop Synchronizer:

- An extension of the double flop synchronizer with an additional flip-flop.

- Provides even more time for metastability resolution.

- Pros: Higher reliability than double flop.

- Cons: Increased latency and area overhead.

- Gray Code Counters:

- Used for transferring multi-bit counters across clock domains.

- Only one bit changes at a time, reducing the risk of capturing an invalid state.

- Pros: Effective for counter transfers.

- Cons: Limited to specific use cases (counters).

- Handshaking Protocols:

- Implements a request-acknowledge mechanism between clock domains.

- Ensures data is only transferred when both domains are ready.

- Pros: Reliable for multi-bit data transfer.

- Cons: Can be complex to implement and may introduce significant latency.

- FIFO (First-In-First-Out) Buffers:

- Used for transferring multiple data items or streams across clock domains.

- Separate read and write pointers operate in different clock domains.

- Pros: Efficient for high-bandwidth data transfer.

- Cons: Requires careful design of full/empty flags and pointer synchronization.

- Pausible Clocks:

- Temporarily pauses the receiving clock to allow more time for metastability resolution.

- Pros: Can be very effective in certain designs.

- Cons: Complex to implement and can affect overall system timing.

- Synchronous Design Techniques:

- Using techniques like clock gating or muxing to create pseudo-synchronous interfaces.

- Pros: Can simplify CDC in some cases.

- Cons: May not be suitable for all design scenarios.

- Metastability-Hardened Flip-Flops:

- Using specially designed flip-flops with improved metastability characteristics.

- Pros: Can improve overall system reliability.

- Cons: May not be available in all technology libraries.

- Clock Domain Partitioning:

- Minimizing the number of CDC paths in the design through careful architecture planning.

- Pros: Reduces overall CDC complexity.

- Cons: May require significant architectural changes.

- Formal Verification Techniques:

- Using formal methods to prove the correctness of CDC implementations.

- Pros: Can provide high confidence in CDC robustness.

- Cons: Requires specialized tools and expertise.

The choice of method depends on factors such as the specific design requirements, performance needs, area constraints, and the nature of the data being transferred across clock domains.

How do you ensure reliable data transfer between asynchronous clock domains?

Sample Question: What strategies and techniques do you employ to guarantee reliable data transfer across asynchronous clock domains?

Expert Answer: Ensuring reliable data transfer between asynchronous clock domains requires a multi-faceted approach. Here are key strategies and techniques:

- Double or Triple Flop Synchronizers:

- Single-Bit Signals: For single-bit signals, use double or triple flop synchronizers to cross the clock domain boundary. This reduces the risk of metastability by allowing the signal to settle before being sampled by the destination clock domain.

- Gray Code for Multi-Bit Counters:

- Multi-Bit Signals: When transferring multi-bit counters or pointers, use Gray code encoding. Gray code ensures that only one bit changes at a time, reducing the risk of capturing an invalid state during the transition.

- Handshaking Protocols:

- Controlled Data Transfer: Use handshaking protocols like Ready/Valid or Request/Acknowledge to control the flow of data between domains. This ensures that data is only transferred when both domains are ready.

- Asynchronous FIFOs:

- High-Bandwidth Data Transfer: Use asynchronous FIFOs (First-In-First-Out) for high-bandwidth data transfer between asynchronous clock domains. The FIFO uses separate read and write pointers, which are synchronized across the clock domains.

- Pointer Encoding: Use Gray code for the read and write pointers to ensure that the pointers are correctly interpreted in both clock domains.

- Data Validity Signaling:

- Ensure Data Stability: Implement a data validity signaling mechanism to ensure that the receiving clock domain only processes data when it is stable and valid. This can be done using handshake signals or dedicated validity flags.

Example:

always @(posedge dest_clk or posedge reset) begin

if (reset) begin

data_valid_sync <= 1'b0;

end else begin

data_valid_sync <= data_valid;

end

end

always @(posedge dest_clk or posedge reset) begin

if (reset) begin

data_reg <= 0;

end else begin

if (data_valid_sync) begin

data_reg <= data_in;

end

end

end

Example:

// Write Pointer (Gray Code)

always @(posedge wr_clk or posedge reset) begin

if (reset) begin

wr_ptr_bin <= 0;

end else begin

wr_ptr_bin <= wr_ptr_bin + 1;

end

end

assign wr_ptr_gray = bin2gray(wr_ptr_bin);

// Read Pointer (Gray Code)

always @(posedge rd_clk or posedge reset) begin

if (reset) begin

rd_ptr_bin <= 0;

end else begin

rd_ptr_bin <= rd_ptr_bin + 1;

end

end

assign rd_ptr_gray = bin2gray(rd_ptr_bin);

Example (Ready/Valid):

always @(posedge src_clk or posedge reset) begin

if (reset) begin

data_valid <= 1'b0;

end else begin

if (src_ready) begin

data_valid <= 1'b1;

end

end

end

always @(posedge dest_clk or posedge reset) begin

if (reset) begin

dest_ready <= 1'b0;

end else begin

if (data_valid) begin

dest_ready <= 1'b1;

end

end

end

Example:

function [N-1:0] bin2gray;

input [N-1:0] bin;

begin

bin2gray = bin ^ (bin >> 1);

end

endfunction

Example:

always @(posedge dest_clk or posedge reset) begin

if (reset) begin

sync_reg1 <= 1'b0;

sync_reg2 <= 1'b0;

end else begin

sync_reg1 <= async_signal;

sync_reg2 <= sync_reg1;

end

end

TalenCat: Master Clock Domain Crossing Interview Questions

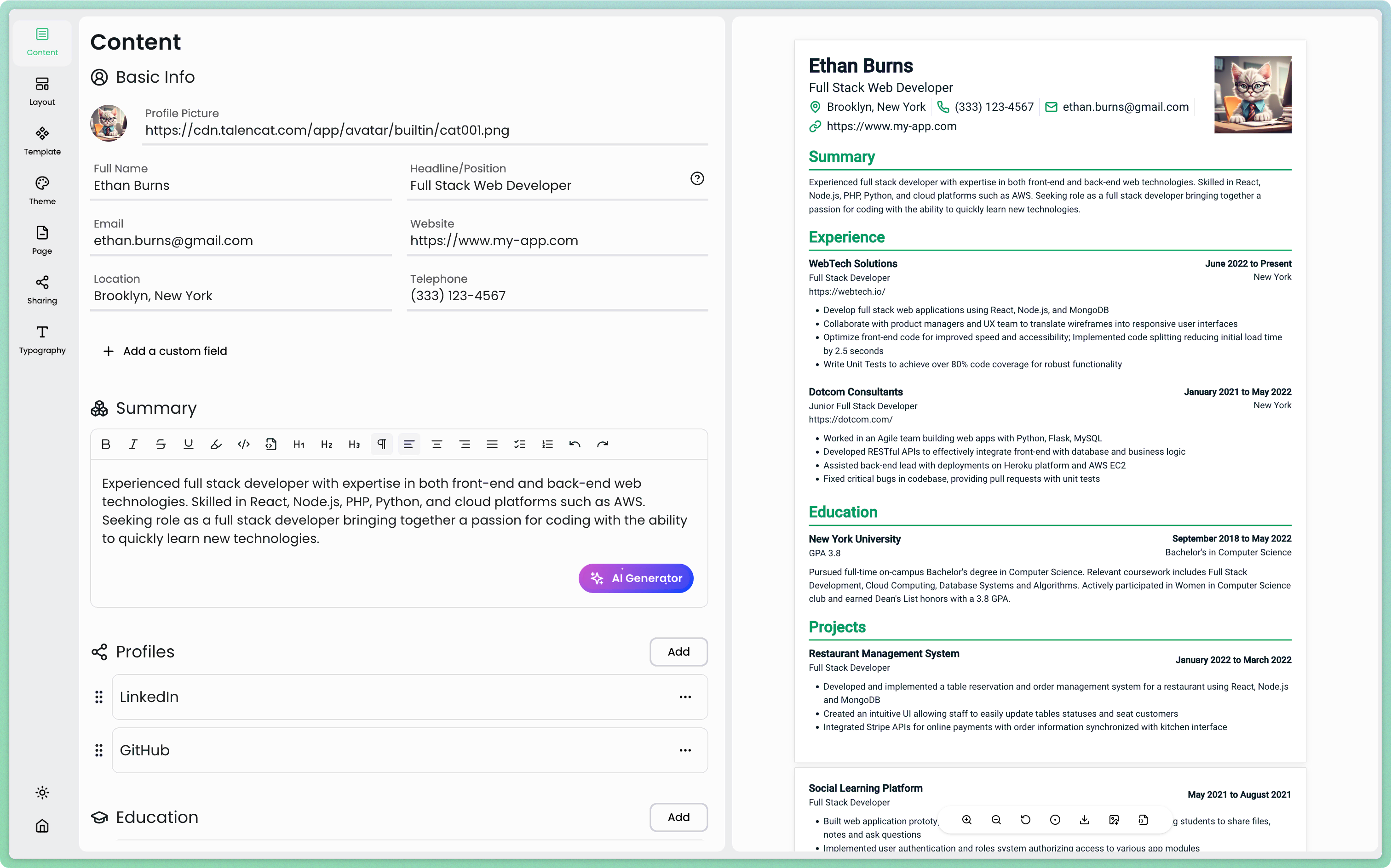

Preparing for an interview that involves clock domain crossing can be challenging. However, with TalenCat CV Maker, you can create a professional resume and generate tailored interview questions to help you ace your next digital design or FPGA engineering interview.

Step 1: Sign up or log in to TalenCat CV Maker. Create a new resume or upload your existing one, focusing on your experience with clock domain crossing and related skills.

Step 2: Navigate to the "AI Assistant" section and select "Interview Assistant" from the left-side menu. This powerful feature will analyze your resume content, particularly focusing on your clock domain crossing expertise.

Step 3: Click "Analyze Now" to generate potential interview questions based on your resume content. TalenCat's AI will focus on your clock domain crossing experience and related skills.

Step 4: Review the generated questions and prepare your answers. These questions will likely cover topics such as synchronization techniques, metastability issues, and clock domain crossing verification methods.

Step 5: Use TalenCat's resume editor to refine your resume based on the generated questions, ensuring you highlight your clock domain crossing expertise effectively.

By leveraging the AI interview tool provided by TalenCat CV Maker, you can confidently prepare for your clock domain crossing interview questions. This online resume builder not only helps you create a standout resume but also equips you with the knowledge of potential interview questions, giving you a significant advantage in your job search.

Remember, thorough preparation is key to acing any technical interview. With TalenCat CV Maker, you're not just creating a resume; you're building a comprehensive strategy for interview success in the field of digital design and FPGA engineering.