In the world of digital design verification, the Universal Verification Methodology (UVM) has become an indispensable tool for ensuring the reliability and functionality of complex electronic systems. As the industry standard for verification, UVM has revolutionized the way engineers approach the challenging task of validating hardware designs. This comprehensive guide aims to equip you with the knowledge and insights necessary to excel in UVM-related interviews, covering everything from fundamental concepts to advanced techniques.

Whether you're a seasoned verification engineer looking to brush up on your UVM skills or a newcomer preparing for your first UVM-focused interview, this article will serve as your go-to resource. We'll explore common interview questions, delve into key UVM components and concepts, and provide expert answers to help you demonstrate your proficiency in this critical methodology.

Introduction to UVM Methodology

The Universal Verification Methodology (UVM) has emerged as a cornerstone in the field of digital design verification, providing a standardized and efficient approach to validating complex hardware designs. As the complexity of electronic systems continues to grow, the importance of robust verification methodologies has never been more pronounced.

What is UVM?

UVM is a standardized methodology for verifying integrated circuit designs. It is based on SystemVerilog and provides a framework for creating flexible, reusable verification components and test environments. UVM builds upon the concepts of its predecessors, such as OVM (Open Verification Methodology) and eRM (e Reuse Methodology), to offer a comprehensive solution for modern verification challenges.

Importance of UVM in Digital Design Verification

The adoption of UVM has brought numerous benefits to the digital design verification process:

- Standardization: UVM provides a common language and structure for verification environments, facilitating collaboration and knowledge sharing across teams and projects.

- Reusability: The modular nature of UVM components allows for easy reuse and adaptation, significantly reducing development time and effort.

- Scalability: UVM's architecture supports the creation of complex, hierarchical testbenches that can scale with increasing design complexity.

- Improved Coverage: The methodology's built-in features for functional coverage and constrained random testing help ensure comprehensive verification of design functionality.

- Industry Support: As an industry standard, UVM enjoys widespread support from EDA tool vendors and a large community of users, ensuring continuous improvement and availability of resources.

Common UVM Interview Questions

Preparing for a UVM interview requires a solid understanding of both theoretical concepts and practical applications. Let's explore some of the most common questions you might encounter, along with expert answers to help you showcase your knowledge.

General UVM Questions

What is UVM and why is it used?

Expert Answer: UVM, or Universal Verification Methodology, is a standardized methodology for verifying integrated circuit designs. It's used because it provides a structured approach to creating reusable and scalable verification environments. UVM helps in reducing verification time, improving code quality, and ensuring comprehensive coverage of design functionality. Its standardization also facilitates collaboration and knowledge sharing across the industry.

Explain the advantages of using UVM.

Expert Answer: UVM offers several key advantages:

- Reusability: UVM components are highly modular and can be easily reused across projects.

- Scalability: The methodology supports the creation of complex, hierarchical testbenches.

- Standardization: UVM provides a common language and structure for verification environments.

- Improved productivity: Pre-defined base classes and utilities speed up testbench development.

- Better coverage: Built-in features for functional coverage and constrained random testing ensure thorough verification.

- Industry support: Wide adoption means extensive resources and tool support are available.

What are the key components of the UVM architecture?

Expert Answer: The key components of UVM architecture include:

- UVM Test: The top-level component that controls the overall test execution.

- UVM Environment: Contains all the verification components.

- UVM Agent: Groups related components like driver, monitor, and sequencer.

- UVM Sequencer: Generates stimulus sequences.

- UVM Driver: Translates transactions into pin-level activity.

- UVM Monitor: Observes and collects information from the DUT interface.

- UVM Scoreboard: Checks the correctness of DUT behavior.

- UVM Configuration Database: Stores and retrieves configuration information.

- UVM Factory: Enables the creation of objects through a centralized mechanism.

UVM Components and Concepts

Understanding the core components and concepts of UVM is crucial for any verification engineer. Let's delve into some specific elements that are often the subject of interview questions.

What is a UVM RAL model?

Expert Answer: A UVM RAL (Register Abstraction Layer) model is a high-level representation of the registers and memory in a design. It provides a convenient way to access and manipulate registers without dealing with low-level details. The RAL model automates the generation of register tests, simplifies the creation of sequences that interact with registers, and helps maintain consistency between the design and verification environments.

What is the role of sequencers in UVM?

Expert Answer: Sequencers in UVM play a crucial role in generating and managing stimulus for the testbench. They act as a bridge between sequences (which define the stimulus) and drivers (which apply the stimulus to the DUT). Sequencers are responsible for arbitrating between multiple sequences, managing priorities, and ensuring that the right stimulus is sent to the driver at the right time. They also handle responses from the driver, allowing for dynamic adjustment of stimulus based on DUT behavior.

Explain TLM ports and exports in UVM.

Expert Answer: TLM (Transaction Level Modeling) ports and exports are communication mechanisms in UVM that allow components to exchange information at a transaction level, abstracting away the details of signal-level communication.

TLM ports are used by components that need to send transactions to other components. They act as the "output" side of the communication channel.

TLM exports, on the other hand, are used by components that receive transactions. They serve as the "input" side of the communication channel.

These constructs enable loose coupling between components, enhancing modularity and reusability in UVM testbenches.

What is an analysis port?

Expert Answer: An analysis port is a specialized TLM port in UVM used for broadcasting transactions to multiple subscribers. Unlike regular TLM ports that typically have a one-to-one connection, analysis ports allow for one-to-many connections. They are commonly used in monitors to distribute observed transactions to multiple analysis components, such as scoreboards or coverage collectors, without those components needing to know about each other.

UVM Phases and Their Functions

UVM phases provide a structured approach to the execution of a testbench. Understanding these phases and their purposes is essential for effective UVM implementation.

Describe the different UVM phases.

Expert Answer: UVM defines several phases for testbench execution:

- Build Phase: Constructs the testbench hierarchy.

- Connect Phase: Establishes connections between components.

- End of Elaboration Phase: Allows for final adjustments to the testbench structure.

- Start of Simulation Phase: Performs any necessary pre-run setup.

- Run Phase: Executes the actual test scenarios.

- Extract Phase: Extracts and processes results.

- Check Phase: Performs final checks on collected data.

- Report Phase: Generates and outputs test reports.

- Final Phase: Performs cleanup operations.

These phases ensure a systematic and orderly execution of the verification process.

How do you start a UVM phase?

Expert Answer: UVM phases are typically started automatically by the UVM framework. However, you can explicitly start a phase using the phase.raise_objection() and phase.drop_objection() methods. This is often done in the run phase to control when the simulation ends. For example:

task run_phase(uvm_phase phase);

phase.raise_objection(this);

// Test logic here

phase.drop_objection(this);

endtask

This ensures that the phase doesn't complete until all objections are dropped.

Which phase refers to the function and which phase is the task?

Expert Answer: In UVM, most phases are implemented as functions, including the build, connect, endofelaboration, startofsimulation, extract, check, report, and final phases. These phases are typically used for setup, configuration, and post-processing activities.

The run phase is implemented as a task. This allows it to consume simulation time and is where the actual test execution and stimulus generation occur. The run phase can include delays, wait statements, and other time-consuming operations.

Advanced UVM Concepts

What is a virtual sequencer in UVM?

Expert Answer: A virtual sequencer is a high-level sequencer in UVM that coordinates multiple lower-level sequencers. It doesn't directly generate transactions but instead manages and orchestrates sequences across different interfaces or protocols. Virtual sequencers are particularly useful in complex testbenches where you need to coordinate stimulus across multiple agents or interfaces. They allow for the creation of higher-level scenarios that involve multiple parts of the DUT simultaneously.

How does factory pattern work in UVM?

Expert Answer: The factory pattern in UVM is a powerful mechanism that allows for the creation of objects without specifying their exact class. It provides a centralized way to create and override types, enabling greater flexibility and reusability in testbench development.

Key aspects of the UVM factory include:

- Registration: Classes are registered with the factory using macros like

uvm_object_utils. - Creation: Objects are created using factory methods like

create()instead of thenew()constructor. - Overriding: The factory allows runtime type overriding, enabling the substitution of extended classes without modifying the original code.

This pattern is crucial for creating modular, extensible testbenches that can be easily customized for different verification scenarios.

What is the difference between a sequence and a sequencer?

Expert Answer: A sequence and a sequencer serve different but complementary roles in UVM:

Sequence: A sequence is a class that defines a series of transactions or stimuli to be sent to the DUT. It encapsulates the logic for generating specific test scenarios or patterns of transactions.

Sequencer: A sequencer is a component that manages and executes sequences. It acts as an arbiter between multiple sequences and the driver, determining which sequence gets to send its transactions next.

In essence, sequences define "what" stimulus to generate, while sequencers control "when" and "how" that stimulus is sent to the driver.

Explain the concept of 'uvmsequenceutils'.

Expert Answer: uvm_sequence_utils is a macro in UVM used to register a sequence with the factory and to declare utility functions for that sequence. It's typically used in older UVM code or for backward compatibility.

In modern UVM (1.2 and later), uvm_sequence_utils is largely replaced by uvm_object_utils for sequences. The newer macro provides the same functionality but is more consistent with the naming conventions used for other UVM objects.

Using uvm_object_utils for sequences allows them to be created via the factory, enables field automation for printing and comparing, and provides other utility functions that are useful for managing sequences in a UVM testbench.

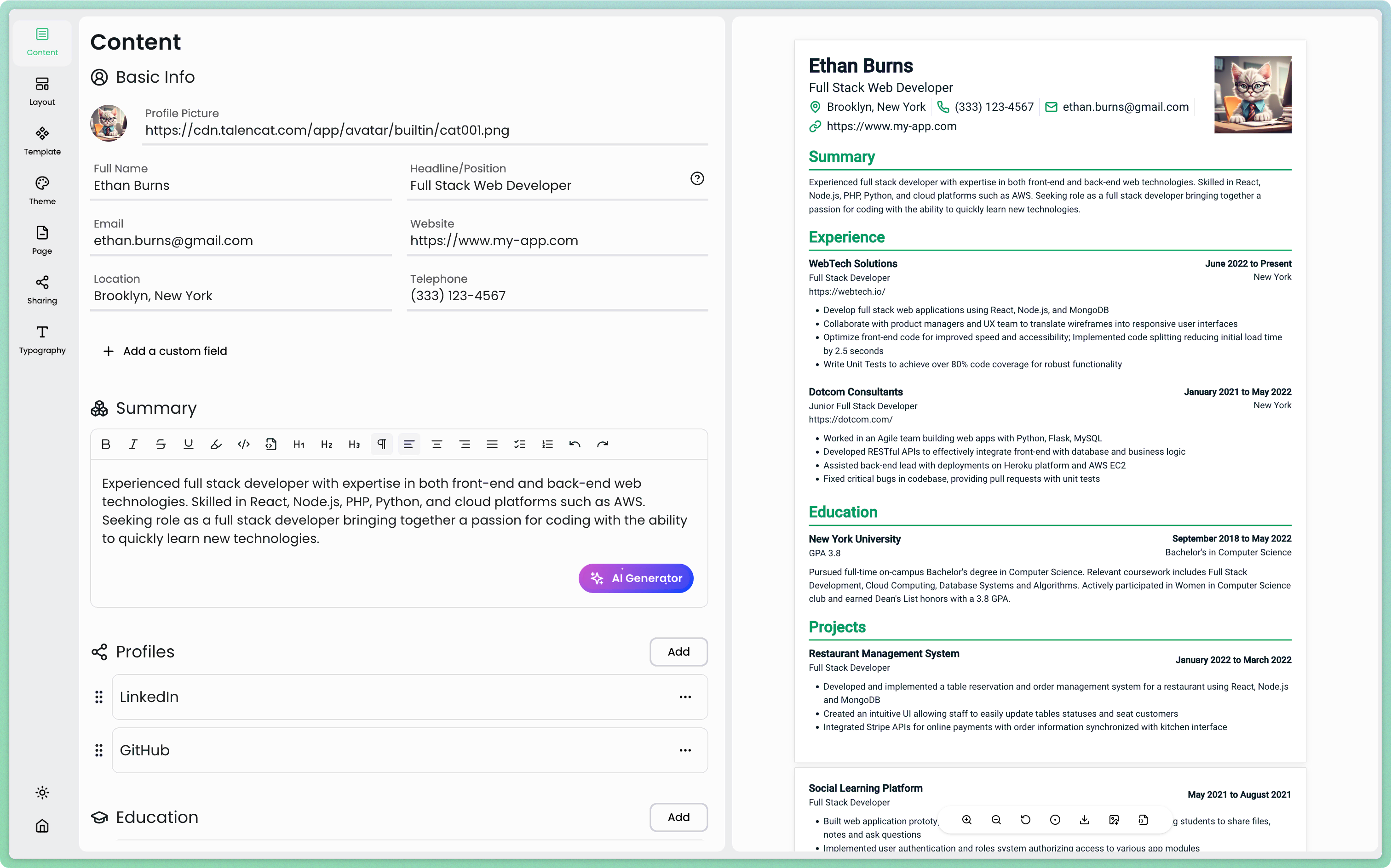

Mastering UVM Methodology Interview Questions with TalenCat CV Maker

Preparing for an interview focused on UVM (Universal Verification Methodology) can be challenging, but with the right tools, you can significantly boost your confidence. TalenCat CV Maker, an advanced online resume builder, offers a unique feature to help you navigate potential UVM methodology interview questions derived from your resume.

Here's how to use TalenCat CV Maker to prepare for your UVM methodology interview:

Step 1: Log in to TalenCat CV Maker and create or upload your resume focusing on your UVM methodology experience.

Step 2: Navigate to the "AI Assistant" section and select "Interview Assistant" from the left-side menu. This powerful feature will analyze your resume content, focusing on your UVM methodology skills and experiences.

Step 3: Click "Analyze Now" to generate potential UVM methodology interview questions based on your resume content.

Step 4: Review the generated questions, which may include topics such as:

- Your experience with UVM components (e.g., sequencers, drivers, monitors)

- Implementing complex testbenches using UVM

- Challenges you've faced in UVM-based verification projects

- Your understanding of UVM phases and their importance

Step 5: Use TalenCat's AI-powered interface to refine and practice your answers to these UVM-specific questions.

By leveraging TalenCat CV Maker's Interview Assistant, you can thoroughly prepare for your UVM methodology interview, ensuring you're ready to showcase your expertise and experience in this critical verification framework.

Remember, the key to acing your UVM methodology interview lies in thorough preparation and the ability to articulate your experiences clearly. With TalenCat CV Maker, you're not just creating a resume; you're building a comprehensive strategy for interview success in the field of UVM-based verification.

Example UVM Interview Questions

Sample Questions with Answers

What is the role of configuration in UVM?

Expert Answer: Configuration in UVM plays a crucial role in creating flexible and reusable testbench components. It allows for the separation of component structure from its configuration, enabling the same component to be used in different scenarios with different settings.

Key aspects of UVM configuration include:

- Configuration Objects: These are used to store configuration parameters for components.

- Configuration Database: A global database that allows setting and retrieving configuration information.

- set/getconfig* methods: Used to set and retrieve configuration items.

For example, you might use configuration to set the number of transactions a driver should send, or to specify the address range a monitor should observe. This approach allows for easy modification of component behavior without changing the component's code, enhancing reusability and maintainability of the testbench.

How can you implement a scoreboarding mechanism in UVM?

Expert Answer: Implementing a scoreboarding mechanism in UVM typically involves the following steps:

- Create a Scoreboard Class: Derive from uvm_scoreboard and implement the necessary logic.

- Define Prediction Logic: Implement a method to predict expected results based on input transactions.

- Implement Comparison Logic: Create a method to compare predicted results with actual results from the DUT.

- Use Analysis Ports: Connect the scoreboard to monitors using analysis ports to receive transactions.

- Handle Transactions: In the write() method of the analysis export, process incoming transactions, make predictions, and perform comparisons.

- Report Results: Use UVM reporting mechanisms to log mismatches or successful comparisons.

Here's a basic example structure:

class my_scoreboard extends uvm_scoreboard;

`uvm_component_utils(my_scoreboard)

uvm_analysis_export #(my_transaction) exp_export;

uvm_analysis_export #(my_transaction) act_export;

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

exp_export = new("exp_export", this);

act_export = new("act_export", this);

endfunction

function void write_exp(my_transaction tr);

// Make prediction based on input transaction

endfunction

function void write_act(my_transaction tr);

// Compare actual result with prediction

// Report any mismatches

endfunction

endclass

Describe how to handle randomization in UVM sequences.

Expert Answer: Randomization in UVM sequences is a powerful technique for generating diverse and comprehensive test scenarios. Here's how you can effectively handle randomization in UVM sequences:

- Define Randomizable Fields: Use the

randkeyword to declare fields that should be randomized. - Add Constraints: Use constraint blocks to define valid ranges or relationships between randomized fields.

- Use the

randomize()Method: Callrandomize()in thebody()task of your sequence to randomize the fields before creating a transaction. - Handle Randomization Failures: Use

if (!randomize())to check for and handle randomization failures. - Utilize Randomization Methods: Take advantage of SystemVerilog's randomization methods like

rand_mode(),constraint_mode(), andrandomize() withfor fine-grained control.

Best Practices for UVM Interviews

How to Prepare for UVM Interviews

- Review UVM Fundamentals: Ensure you have a solid grasp of UVM basics, including components, phases, and communication mechanisms.

- Practice Coding: Write and debug UVM testbenches to gain practical experience.

- Study Design Patterns: Understand common design patterns used in UVM.

- Analyze Real-World Examples: Examine open-source UVM testbenches.

- Stay Updated: Keep abreast of the latest developments in UVM and SystemVerilog.

Tips for Answering UVM Questions

- Listen Carefully: Ensure complete understanding of questions before responding.

- Provide Context: Explain the importance and relevance of concepts.

- Use Examples: Illustrate points with practical examples.

- Structure Responses: Organize answers logically and clearly.

- Show Problem-Solving Skills: Demonstrate how you approach challenges.

Resources for Further Study

- Official UVM Documentation

- Online UVM Tutorials and Courses

- Technical Forums and Discussion Groups

- Industry Conferences and Webinars

- UVM Reference Books and Publications

Conclusion

Recap of UVM Methodology Importance

UVM remains the industry standard for hardware verification, providing:

- Standardized approach to verification

- Reusable components and methodologies

- Comprehensive coverage capabilities

- Robust debugging features

- Industry-wide support and resources

Encouragement for Continuous Learning in UVM

- Stay current with UVM developments

- Practice implementing various verification scenarios

- Engage with the verification community

- Build a portfolio of verification projects

- Pursue certification and training opportunities